# Signetics

**Microprocessor Products**

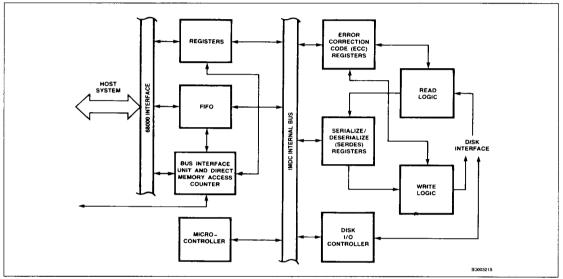

## DESCRIPTION

The SCN68454 Intelligent Multiple Disk Controller (IMDC) provides the traditional and advanced features required to control Winchester type rigid disks and floppy disks. It can control up to four rigid or floppy disk drives, in any combination. It can be used to control, with a minimum of external hardware, any drive that has an SA1000 interface standard or an ST506 Seagate interface standard.

The IMDC supports soft or hard sectored disk track format and standard IBM track formats for floppy disks (both single and double density).

The controller is programmable via an external host processor by the use of high level commands. Data transfer on the host data bus can be 8 or 16-bit in parallel. The IMDC is capable of handling a serial data rate of up to 10Mbits per second. The SCN68454 is constructed using Signetics MOS-VLSI technology.

#### FEATURES

- Bus compatible with SCN68000

microprocessor

- Automatic rerun on bus error

- Supports SCN68000 vectored interrupts

- 31-bit address counter

- 16/8-bit data transfers

- Supports up to 4 rigid disks and floppy disks in any combination

- Supports SA1000 and ST506 Winchester interfaces

- Data rates up to 10Mbits per second for MFM

- Data rates up to 2Mbits per second for FM

- Handles FM and MFM data encoding/decoding

# SCN68454 Intelligent Multiple Disk Controller (IMDC)

**Preliminary Specification**

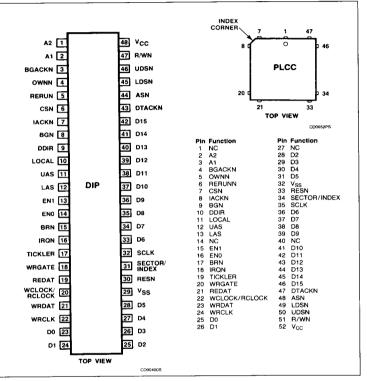

## PIN CONFIGURATION

- On chip DMA controller and FIFO buffer (128 bytes)

- Multiple sector read/write with implied seek

- Automatic bad sector handling

- 32 and 40-bit ECC programmable polynomials

- Supports computer generated ECC polynomials

January 1986

# SCN68454

Preliminary Specification

## ORDERING CODE

| PACKAGES    | $V_{CC} = 5V \pm 5\%$ , $T_A = 0$ to 70°C |

|-------------|-------------------------------------------|

| Ceramic DIP | SCN68454C6148                             |

| Plastic DIP | SCN68454C6N48                             |

| Plastic LCC | SCN68454C6A52                             |

## **BLOCK DIAGRAM**

### PIN DESCRIPTION

The pin description table describes the function of each of the pins of the IMDC. Signal names ending in 'N' are active low. All other signals are active high. In the descriptions, 'REG mode' refers to the state when the IMDC is chip selected. The term 'DMA mode' refers to the state when the IMDC assumes ownership of the bus. The term 'LOCAL mode' refers to the state when the IMDC is transferring data to or from the disk interface. The IMDC is in the 'IDLE mode' at all other times.

In this data sheet, signals are discussed using the terms 'active' and 'inactive' or 'asserted' and 'negated' independent of whether the signal is active in the high (logic one) state or the low (logic zero) state. Refer to the individual pin descriptions for the definition of the active level of each signal.

|          | PIN NO.             |                                            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------------------|--------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC | DIP                 | PLCC                                       | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A1, A2   | 1, 2                | 2, 3                                       | 1/0  | Address Lines: Active high, three-statable. In the REG mode, these low order address lines specify which internal register of the IMDC is being accessed. In DMA mode, A1 – A2 are outputs which provide the low order address bits of the location being accessed. Three-stated in IDLE and LOCAL mode.                                                                                                                                                                                                                                                         |

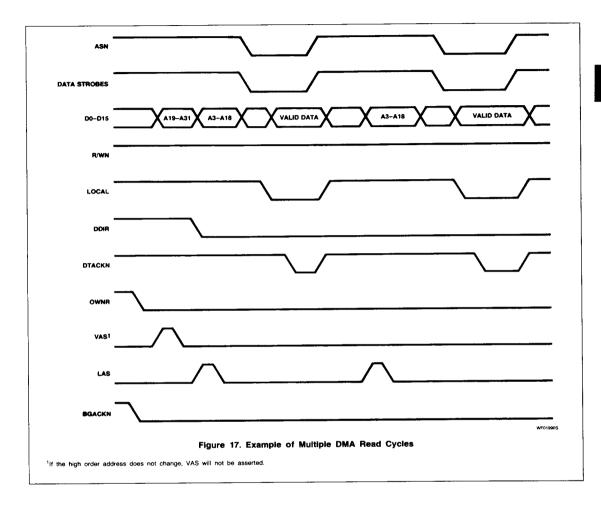

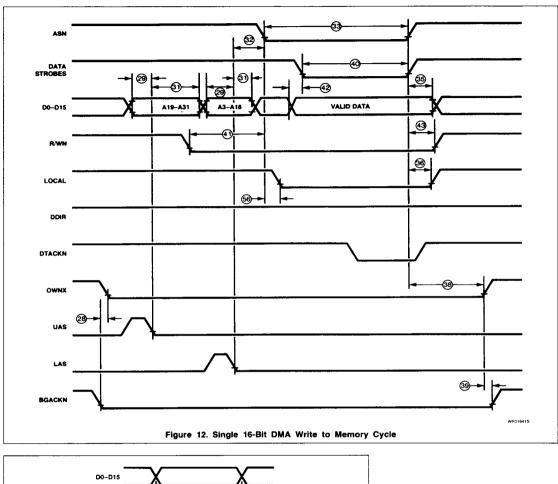

| D0 – D15 | 23 - 28,<br>33 - 42 | 25, 26,<br>28 – 31,<br>36 – 39,<br>41 – 46 | 1/0  | <b>Data Lines:</b> Active high, three-statable. In REG mode, the bidirectional data lines are used to transfer data between the CPU and the IMDC registers. In LOCAL mode, the bidirectional data lines are used to transfer data between the IMDC and the disk unit (three-stated in IDLE mode). In DMA mode, the data lines carry the address information. During the first part of the cycle, $D0 - D15$ provide high order address bits, $A19 - A31$ , which are latched by UAS. The data lines then provide A3 - A18 address bits which are latched by LAS. |

January 1986

## Signetics Microprocessor Products

# Intelligent Multiple Disk Controller (IMDC)

## **PIN DESCRIPTION (Continued)**

|          | PIN | NO.  |      | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC | DIP | PLCC | TYPE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

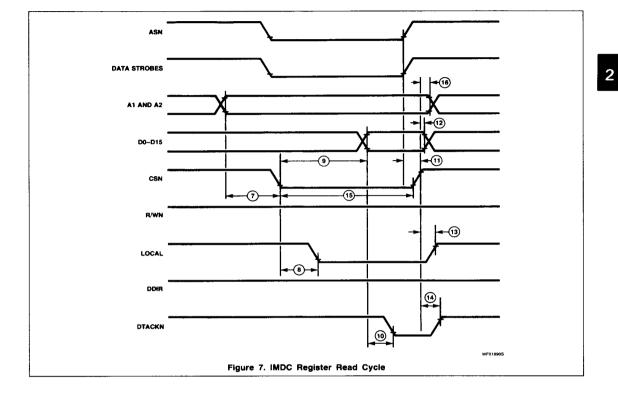

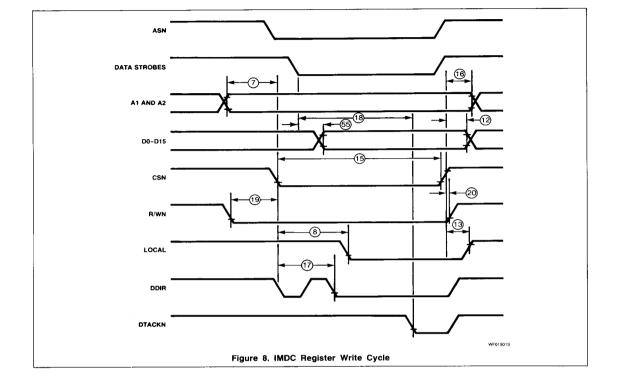

| ASN      | 44  | 48   | 1/0  | Address Strobe: Active low, three-statable. In REG and IDLE modes, ASN is an input which<br>indicates that the current bus master has placed a valid address on the bus. It is monitored by the<br>IMDC during bus arbitration to ascertain that the previous bus master has completed the current<br>bus cycle. In DMA mode, it is an output indicating that the IMDC has placed a valid address on<br>the bus.                                                                                                                                                                     |

| UDSN     | 46  | 50   | 1/0  | Upper Data Strobe: Active low, three-statable. In REG and IDLE modes, UDSN is an input which indicates that the upper data byte of the addressed word is being addressed. In DMA mode, it is an output with the same meaning. In an eight bit system this input is tied to DSN.                                                                                                                                                                                                                                                                                                      |

| LDSN     | 45  | 49   | 1/0  | Lower Data Strobe: Active low, three-statable. In REG and IDLE modes, LDSN is an input which indicates that the lower data byte of the addressed word is being addressed. In DMA mode, it is an output with the same meaning. In an eight bit system this input is tied to A0.                                                                                                                                                                                                                                                                                                       |

| R/WN     | 47  | 51   | 1/0  | <b>Read/Write:</b> Active high for read, low for write, three-statable. In REG mode, R/WN is an input which controls the direction of data flow through the IMDC's input/output data bus interface and through an external data bus buffer. R/WN high causes the IMDC to place the data from the addressed register on the data bus, while R/WN low causes the IMDC to accept data from the data bus. In DMA mode, R/WN is an output to memory and I/O controllers indicating the type of bus cycle. It is held three-stated during IDLE and LOCAL mode.                             |

| CSN      | 6   | 7    | 1    | Chip Select: Active low. When low, places the IMDC into the REG mode. This input signal is used to select the IMDC for register data transfers. These transfers take place over the D0 – D15 lines as controlled by the R/WN and A1 – A2 inputs. The IMDC is deselected when CSN is high. CSN is ignored during DMA mode.                                                                                                                                                                                                                                                            |

| DTACKN   | 43  | 47   | 1/0  | <b>Data Transfer Acknowledge:</b> Active low, three-statable. In REG mode, DTACKN is asserted on a write cycle to indicate that the data on the bus has been latched, and on a read cycle or interrupt acknowledge cycle to indicate that valid data is present on the bus. The signal is negated (driven high) when completion of the cycle is indicated by negation of the CSN or IACKN input. In DMA mode, DTACKN is an input monitored by the IMDC to determine when the addressed device (memory) has latched the data (write cycle) or put valid data on the bus (read cycle). |

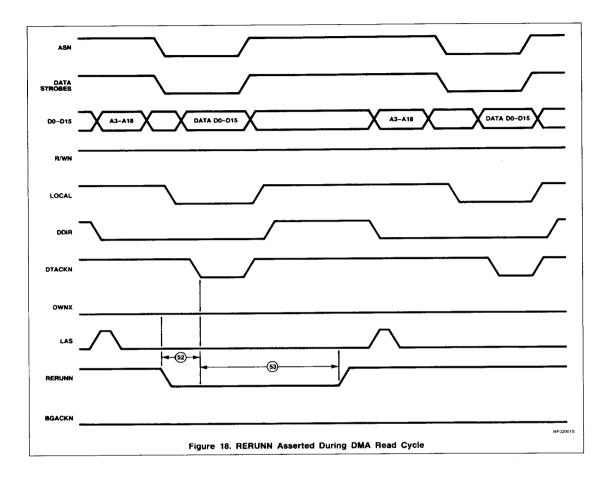

| RERUNN   | 5   | 6    |      | <b>Rerun:</b> Active low. This input is asserted by external error detect logic to indicate a bus error. In DMA mode, the IMDC stops operation and three-states the data, address, and control lines, except BGACKN. It remains IDLE until RERUNN becomes inactive, and then retries the last bus cycle. If RERUNN is asserted again, the IMDC sets the error code in the main status byte, stops DMA operation, releases the bus, and interrupts the CPU. Not monitored in REG, LOCAL and IDLE modes.                                                                               |

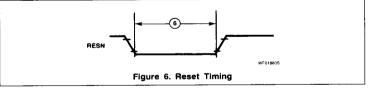

| RESN     | 30  | 33   | I    | Master Reset: Active low. Assertion of this pin clears the internal registers and initializes the interrupt vector register to H'OF'. All bidirectional I/O lines are three-stated and the IMDC is placed in the IDLE mode.                                                                                                                                                                                                                                                                                                                                                          |

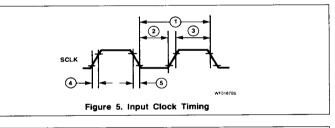

| SCLK     | 32  | 35   |      | <b>Clock:</b> Active high. Usually the system clock, but may be any clock meeting the electrical specifications. Used by the IMDC to synchronize disk functions and external control lines, and may not be gated off at any time. The frequency should be 16MHz $\pm$ 1%.                                                                                                                                                                                                                                                                                                            |

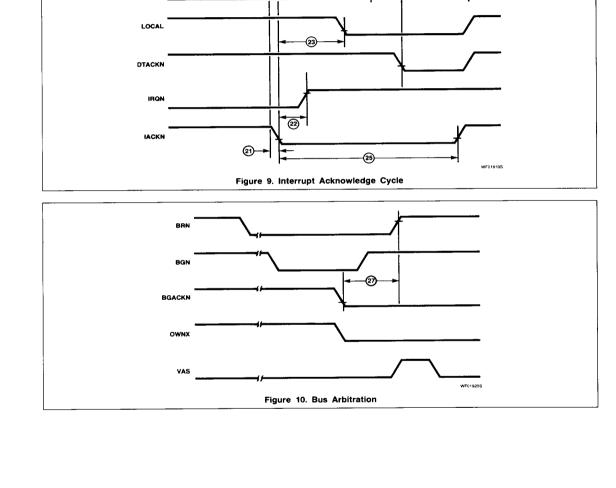

| IRQN     | 16  | 18   | 0    | Interrupt Request: Active low, open drain. This output is asserted at the end of each command<br>execution. The CPU can read the status register to determine the interrupting condition, or can<br>respond with an interrupt acknowledge cycle to cause the IMDC to output an interrupt vector on<br>the data bus.                                                                                                                                                                                                                                                                  |

| IACKN    | 7   | 8    | I    | Interrupt Acknowledge: Active low. When asserted, indicates that the current cycle is an interrupt acknowledge cycle. The IMDC normally responds by placing the contents of the interrupt vector register on the data bus and asserting DTACKN.                                                                                                                                                                                                                                                                                                                                      |

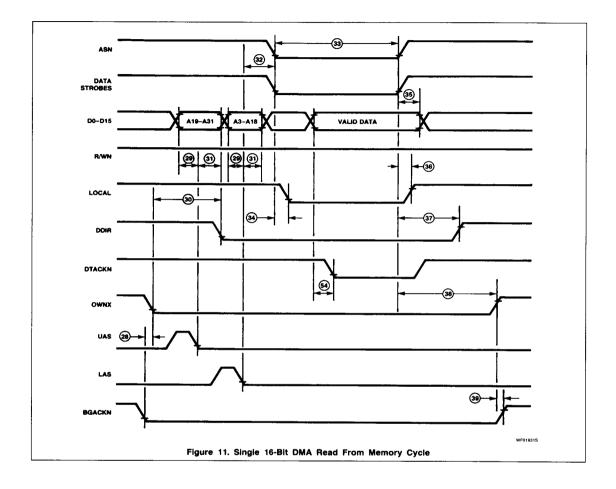

| BRN      | 15  | 17   | 0    | Bus Request: Active low, open drain. BRN is asserted by the IMDC to request ownership of the<br>bus for a DMA transfer. It is negated when the bus has been granted (BGN low) and BGACKN<br>has been asserted.                                                                                                                                                                                                                                                                                                                                                                       |

| BGN      | 8   | 9    | 1    | Bus Grant: Active low. BGN indicates to the IMDC that it is to be the next bus master. After BGN is asserted, the IMDC waits until DTACKN, ASN, and BGACKN have become inactive before assuming ownership of the bus by asserting BGACKN.                                                                                                                                                                                                                                                                                                                                            |

| BGACKN   | 3   | 4    | 1/0  | Bus Grant Acknowledge: Active low, open drain. As an input, BGACKN is monitored by the IMDC during the bus arbitration cycle to determine when it can assume ownership of the bus (BGACKN negated). In DMA mode, it is asserted by the IMDC to indicate that it is the bus master. Three-stated in REG, LOCAL, and IDLE modes.                                                                                                                                                                                                                                                       |

January 1986

SCN68454

2

# SCN68454

### **PIN DESCRIPTION (Continued)**

|                   | PIN | NO.  |      | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                        |

|-------------------|-----|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC          | DIP | PLCC | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                        |

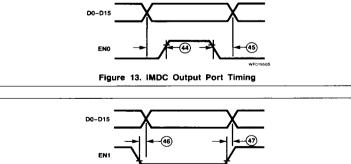

| ENO               | 14  | 16   | 0    | Enable 0: Active high. This signal is asserted during LOCAL mode when the IMDC transmits disk control signals on the data lines D0 - D15. The assertion or negation of EN0 is used to latch the control signals at the disk interface.                                                                                                                   |

| EN1               | 13  | 15   | 0    | Enable 1: Active low. This signal is asserted during LOCAL mode when the IMDC reads the status of the disk drive. The assertion of EN1 is used to enable the status information onto data lines D0 – D15.                                                                                                                                                |

| UAS               | 11  | 12   | 0    | Upper Address Strobe: Active high. UAS is active only during DMA mode. It is used to latch the upper address bits A19 – A31 from the address/data lines.                                                                                                                                                                                                 |

| LAS               | 12  | 13   | 0    | Lower Address Strobe: Active high. LAS is active only during DMA mode. It is used to latch the lower address bits A3 – A18 from the address/data lines.                                                                                                                                                                                                  |

| REDAT             | 19  | 21   |      | Composite Read Data: This signal is the composite disk data synchronized to the RCLOCK signal generated by the external PLL.                                                                                                                                                                                                                             |

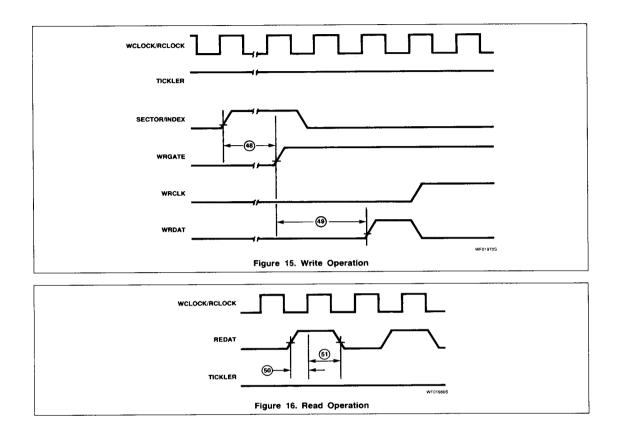

| WRGATE            | 18  | 20   | 0    | Write Gate: Active high. This signal is asserted during disk write operations. Disasserted during all other modes.                                                                                                                                                                                                                                       |

| WCLOCK/<br>RCLOCK | 20  | 22   |      | Write Clock/Read Clock: This clock input is generated by external logic such as the SCB68459<br>DPLL. During disk write operations, the input is defined as WCLOCK which provides the bit-cell<br>frequency to the IMDC. The input is defined as RCLOCK during disk read operations. RCLOCK is<br>twice the data frequency and is synchronized to REDAT. |

| WRDAT             | 21  | 23   | 0    | Write Data Pattern: Active high. This signal provides the write data pattern for external logic, like the SCB68459 DPLL, to use with WRCLK and WCLOCK to generate the write data pulse stream to a disk unit. WRDAT is an non-return to zero (NRZ) signal which changes state on the rising edge of WCLOCK.                                              |

| WRCLK             | 22  | 24   | 0    | Write Clock Pattern: Active high. This signal provides the write clock pattern for external logic,<br>like the SCB68459 DPLL, to use with WRDAT and WCLOCK to generate the write data pulse<br>stream to a disk unit. WRCLK is an NRZ signal which changes state on the rising edge of<br>WCLOCK.                                                        |

| TICKLER           | 17  | 19   | o    | <b>Tickler:</b> Active high. This signal is used to control an external PLL. When TICKLER is asserted, the external PLL should output the crystal controlled clock to the WCLOCK/ RCLOCK input. With TICKLER is low, the PLL should synchronize on the incoming disk data and generate read clock to the WCLOCK/RCLOCK input.                            |

| SECTOR/<br>INDEX  | 31  | 34   |      | Sector/Index: Active high. The IMDC uses the rising edge of the signal to generate the read/<br>write sequence. Hard sectored disk drives output a pulse for each sector boundary for the IMDC.<br>Soft sectored disk drives have a once around index pulse to define the start of a track.                                                              |

| LOCAL             | 10  | 11   | 0    | Local: Active high. During LOCAL mode, this line controls the output enable on the bidirectional buffers of the address/data lines.                                                                                                                                                                                                                      |

| OWNN              | 4   | 5    | 0    | <b>Own:</b> Active low. This output is asserted by the IMDC during the DMA mode to indicate bus mastership. It can be used to enable external address/data and control buffers. Inactive in REG and IDLE modes.                                                                                                                                          |

| DDIR              | 9   | 10   | 0    | <b>Data Direction:</b> Active high. This signal is active during the DMA and REG modes. It controls the direction of the data through the bidirectional buffers on the address/data bus. DDIR is asserted during a read operation of the IMDC.                                                                                                           |

| V <sub>CC</sub>   | 48  | 52   | 1    | +5 volt ± 5% power input.                                                                                                                                                                                                                                                                                                                                |

| Vss               | 29  | 32   | 1    | Power ground input.                                                                                                                                                                                                                                                                                                                                      |

#### REGISTERS

#### **Register Map**

The IMDC is a memory transfer oriented device with minimal information transferred to the registers. The internal accessible register organization of the IMDC is shown in table 1. Register bit formats are shown in table 2. Each is 8-bits wide to allow interface to either 8 or 16-bit host systems. When the IMDC is interfaced to an eight bit system, A0 is tied to LDSN and the data strobe (DSN) is tied to UDSN.

Interrupt Source Register (ISR)

These bits are used to indicate which drive was the source of a command completion interrupt. Bit 4 reflects drive 0 as the source and bit 7 is for drive 3. The assertion of RESN will initialize all four bits to zero. The IMDC will not initiate the next command, if pending, until the host resets the interrupt source bit. The host should also reset the appropriate busy bit in the status and configuration register.

# Drive Status and Configuration Register (DSCR)

#### [0]8/16 Bit Mode

This bit sets the length of memory and register data transfers. Byte transfers are initiated when bit 0 is set to zero. This bit is set to zero when RESN is asserted.

#### [7:4]Drive Busy

These bits are used by the host system to initiate an IMDC command operation for a particular drive. Bit 4 is used for drive 0 and bit 7 for drive 3. After the host system has set a busy bit to activate a drive, the IMDC

January 1986

#### Table 1. IMDC ADDRESS MAP

| ADDRESS<br>BITS <sup>1</sup> | ACRONYM | REGISTER NAME                           | MODE | AFFECTED<br>BY RESET |

|------------------------------|---------|-----------------------------------------|------|----------------------|

| 210                          |         |                                         |      |                      |

| 000                          | EPH     | ECA pointer high                        | R/W  | Yes                  |

| 001                          | EPMH    | ECA pointer middle high                 | R/W  | Yes                  |

| 010                          | EPML    | ECA pointer middle low                  | R/W  | Yes                  |

| 011                          | EPL     | ECA pointer low                         | R/W  | Yes                  |

| 100                          | IVR     | Interrupt vector register               | R/W  | Yes                  |

| 101                          | ISR     | Interrupt source register               | R/W  | Yes                  |

| 1 1 0 <sup>2</sup>           | DSCR    | Drive status and configuration register | R/W  | Yes                  |

| 111                          |         | Reserved                                |      |                      |

NOTES:

1. A0 = 0 for UDSN asserted, A0 = 1 for LDSN asserted for 16- bit mode.

2. In 16-bit systems, the data for this register must be in data bits D0-D7.

#### **Table 2. REGISTER BIT FORMATS**

#### INTERRUPT SOURCE REGISTER

| BIT 7      | BIT 6      | BIT 5      | BIT 4      | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------------|------------|------------|------------|-------|-------|-------|-------|

| DR3<br>INT | DR2<br>INT | DR1<br>INT | DR0<br>INT | <     | NOT   | USED  | >     |

## DRIVE STATUS AND CONFIGURATION REGISTER

| BIT 7       | BIT 6       | BIT 5       | BIT 4       | BIT 3 | BIT 2        | BIT 1 | BIT 0        |

|-------------|-------------|-------------|-------------|-------|--------------|-------|--------------|

| DR3<br>BUSY | DR2<br>BUSY | DR1<br>BUSY | DR0<br>BUSY | <     | - NOT USED - | >     | 8/16<br>MODE |

responds by accessing the corresponding event control area (ECA) and performing the requested action. The host system can abort the current drive operation by resetting the busy bit before the operation is completed. The assertion of RESN will initialize the busy bits to zero (only time the IMDC writes into this register).

## Event Control Area Pointer Registers

(EPH/EPMH/EPML/EPL)

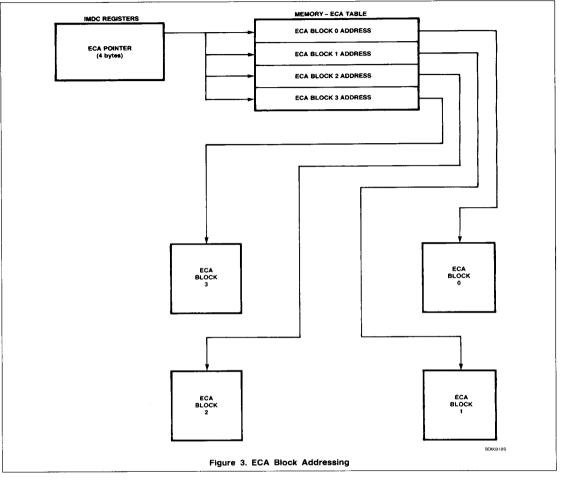

These four registers are used by the host system to direct the IMDC to a table of pointers. The table consists of four 2 word addresses that point to the location of the four ECA blocks. The pointers are arranged in ascending order by drive number. EPL is the least significant byte and EPH the most significant byte. All four registers are cleared to zero by RESN asserted.

#### Interrupt Vector Register (IVR)

The IVR contains the value to be placed on the data bus upon receipt of an interrupt acknowledge from the CPU. The contents of this register are initialized to H'OF' by a reset.

#### OPERATION

The IMDC is an intelligent controller with onchip microprogrammed CPU and interface circuitry. Two interfaces are provided, one to the host CPU and the other to the disk drive. The host interface contains a complete DMA

January 1986

interface compatible with the SCN68000 bus. After the IMDC accepts a command, the DMA interface handles all transfers between the system memory and the IMDC. The IMDC signifies through an interrupt signal that the command is completed.

#### **Operation Initiation**

The host must initialize the IMDC before it can process any command requests. The initialization information must be passed from the host to the IMDC control registers. The information consists of the data byte or word transfer mode selected in the drive status and configuration register. The host must also load an interrupt vector to the interrupt vector register and load the event control areas registers with the start location of the ECA pointer table in system memory.

A new command is requested using the drive status and configuration register. The user sets a bit corresponding to the drive to be serviced. This causes the IMDC to start execution of the command for the requested drive. This can be performed as long as the bus is available. The IMDC accepts the request but does not necessarily begin to process it. If the IMDC is currently doing disk data transfers to another disk drive, it will accept the request and treat it as a pending request for disk drive service. It does this in order to prevent forcing the host processor to wait for it to complete its current processing.

2-463

The IMDC will execute parallel seek operations for floppy and SA1000 type disk drives.

Because four different drives can be on line simultaneously, the possibility exists of more than one pending request to appear in the drive status and configuration register. In this situation the IMDC will process the drive requests in ascending order (i.e., 0, 1, 2, and 3) and then start again with drive zero.

It is also the responsibility of the host to insure the drives that are to be controlled are in a ready state prior to issuing commands. Commands issued to drives that are not ready will result in the command being aborted. Also if a command is requested on a drive that goes from ready to not ready, the IMDC will abort the execution of the command. In both cases, an interrupt cycle will be initiated.

When RESN is asserted, the IMDC will go through an internal initialization program which clears the control registers and the interrupt vector will be set to H'OF'. All bus and control lines will be cleared and the IMDC will enter an idle loop.

#### **DMA Operation**

After a command is started, it is executed without further communication with the host system. All memory data transfers are handled automatically by the on chip DMA controller. The IMDC indicates that it wishes to become the bus master by asserting its bus request (BRN) output. The processor ac-

## SCN68454

knowledges the request by asserting its bus grant (BGN) output which puts the bus up for arbitration.

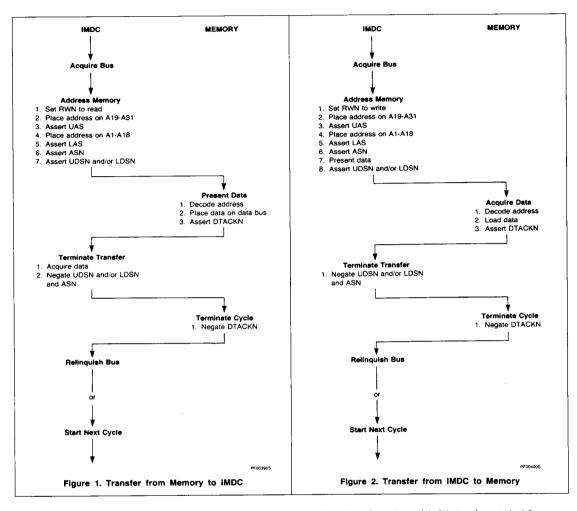

The IMDC will be the next bus master when its BGN input is asserted. The IMDC then waits for address strobe (ASN), data transfer acknowledge (DTACKN), and bus grant acknowledge (BGACKN) to become inactive. It then asserts the BGACKN output to become the bus master and negates the BRN output. The IMDC then proceeds with the transfer of data between itself and memory. After the data transfer phase, the IMDC relinquishes bus mastership by negating the BGACKN output. Flow charts for the transfer operations are shown in figures 1 and 2. Refer to the timing section for the equivalent timing diagrams.

#### **DMA Transfer Rates**

The serial read/write I/O portion of the drive interface is a dedicated slave of the IMDC disk drive interface; that is, a serial string is sent or received by the interface without interruption. The DMA interface, however, must surrender the bus for arbitration after the requested number of operands have been transferred. If the number of transfers does not provide the IMDC with sufficient bus access time, it is conceivable that the DMA may fail to keep track with the disk I/O operation. This situation can occur if the bus is lost for a 'long' period of time. At the IMDC, the serial disk transfer rate is  $1.6\mu$ sec per word at a 10MHz data rate. The IMDC processor operates using a 312.5nsec period clock. Three cycles or 937.5nsec are required to perform one DMA transfer. If the system bus is unavailable to the IMDC DMA for an average time greater than the difference between the drive and DMA transfer rates (662.5nsec), overflow or underflow of the FIFO buffer can result.

As an example, consider a Winchester disk transfer data of 5Mbits/second. If the transfer count is set to 16 words per transfer, the IMDC will transfer each 32 byte block in 15 microseconds. The transfer time will be 51.2 microseconds for the disk data to put 32

#### January 1986

SCN68454

bytes into the FIFO. The difference between the two transfer block rates is 36.2 microseconds. This is the maximum time which the IMDC does not require the system bus.

To avoid this situation the DMA must not lose the bus for a period exceeding the difference in transfer rates. This can be accomplished in a variety of ways. One approach is to allow the DMA to have the bus mastership for the entire sector transfer. A second approach is delay the DMA until a sector has been read into the FIFO buffer and to delay writing to the disk until the FIFO is filled with one sector of data. The first approach severely restricts the availability of the system bus to other devices.

The latter approach requires a minimum FIFO buffer equal to the size of a sector and introduces a delay into the IMDC operation.

As a result, both approaches place stringent limitations on the system and reduce the throughput of the device.

Another alternative is to assign the bus arbitration such that the IMDC always has highest priority and that the bus must be returned in a time segment shorter than the transfer rate difference. This latter solution requires external circuitry to implement and still does not guarantee the IMDC bus access time is sufficient. To provide the user with maximum system flexibility, without severely restricting the bus to other devices, the IMDC has been structured to allow the user to specify the number of operands that the DMA can be master of the bus. The ECA Command Option field permits the user to select the number of operands that can be transferred before the bus is returned for arbitration. This technique allows the user to customize the DMA operation to the needs of the system.

## **I/O DESCRIPTION**

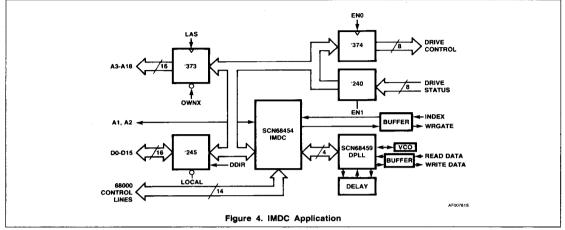

The disk interface consists of two sections. The input and output ports that sense and generate slow changing or static control signals and the serial read/write data section. The parallel data is transferred over the address/ address/data lines (A3/A19/ D0 - A18/A31/D15) during LOCAL mode. Table 3 shows the data bus assignment during an input port bus cycle and table 4 shows the output port bus cycle assignment.

The two signals enable 0 (EN0) and enable 1 (EN1) are used to gate the signals off or onto the bus. EN0 is used to latch the bus during the output cycle and EN1 is used to enable the input data onto the bus.

#### Input Port

The input port consists of eight lines to input disk status information to the IMDC. All signals are active high. To accommodate different drives, signals TROA, TROB, WFA and WFB are used. The IMDC will respond to any one of the signals which becomes active high. The drive will not activate these signal simultaneously.

#### **Output Port**

The output port consists of the signals corresponding to bus lines D0 through D15. All signals are positive logic. A practical implementation of the output port would consist of standard octal registers.

## **EVENT CONTROL AREAS**

The host system communicates with the IMDC through the event control areas (ECAs) which reside in system memory. An ECA parameter block is set up for each disk drive (up to four) to be controlled. These areas contain information that is required by the IMDC to execute a disk command. This information includes data about the requested command and the disk drive. The host prepares for IMDC operation by loading the ECA pointer table in system memory with the address of each of the ECA blocks. The disk drive to ECA block assignment is determined by the relative position of the pointer in the table. The first table entry corresponds to drive zero, the second entry to drive one, etc. (see figure 3).

The IMDC microprogram will use the data contained in the ECA block to generate the disk interface signals and perform the requested drive I/O. Prior to informing the host of a command completion, the

IMDC writes the return status information to the appropriate ECA block memory. Table 5 describes the format of the ECA block.

The communications between the IMDC and the host are established through the ECA. Alteration of the ECA by the host after a command has been accepted by the IMDC is not allowed.

The static and dynamic (see ECA fields) ECA command parameters should be verified by the host before new command execution is requested. During execution of a command involving multiple sectors, it is possible that dynamic values generated by the IMDC could be invalid. The host does not have access during this time to alter or even check these values, therefore, it is the responsibility of the

#### Table 3. INPUT PORT DEFINITION

| BUS LINE | SIGNAL<br>NAME | DEFINITION                                                            |

|----------|----------------|-----------------------------------------------------------------------|

| D0       | INDEX          | Rigid disk index signal (hard sector mode) must be greater than 500ns |

| D1       | READY          | Drive ready                                                           |

| D2       | SEEKC          | Seek completed                                                        |

| D3       | TROA           | Track zero first signal                                               |

| D4       | TR0B           | Track zero second signal                                              |

| D5       | WFA            | Write protection for floppies                                         |

| D6       | WFB            | Write fault                                                           |

| D7 – D15 |                | Not used                                                              |

#### **Table 4. OUTPUT PORT DEFINITION**

| BUS LINE | SIGNAL<br>NAME | DEFINITION                                                                               |

|----------|----------------|------------------------------------------------------------------------------------------|

| D0       | HEAD1          | Head select 2**0/side select for floppy disks set to '0' for single sided floppy disks   |

| D1       | HEAD2          | Head select 2**1                                                                         |

| D2       | HEAD4          | Head select 2**2 that can be transferred                                                 |

| D3       | HEAD8          | Head select 2**3                                                                         |

| D4       | HEAD16         | Head select 2**4                                                                         |

| D5       |                | Not used                                                                                 |

| D6       | STEP           | Step pulse 10µsec long (period set in ECA)                                               |

| D7       | DIR            | Direction of head movement (a high corresponds to head movement toward the disk spindle) |

| D8       | LWC            | Low write current                                                                        |

| D9       | MOT            | Motor on                                                                                 |

| D10      | PRECOM         | Precompensation enable                                                                   |

| D11      | HDL            | Head load for floppy disks                                                               |

| D12      | SEL0           | Drive 0 select                                                                           |

| D13      | SEL1           | Drive 1 select                                                                           |

| D14      | SEL2           | Drive 2 select                                                                           |

| D15      | SEL3           | Drive 3 select                                                                           |

January 1986

host to not only guarantee the integrity of the initial parameters but also to insure that values calculated by the IMDC during the life of a command remain valid. For example, the IMDC cannot know that a calculated DMA address is valid until it attempts to transfer data.

Implied in the execution of any disk operation is reading of the ECA data by the IMDC to load the drive control parameters. At the conclusion of a disk operation, the IMDC performs a write operation to the corresponding ECA parameters to store the results of the command. Both reading and writing of the ECA fields by the IMDC utilize the host/DMA interface to arbitrate for the system bus and to perform the required handshaking.

January 1986

### ECA FIELDS

As an IMDC command proceeds through its execution; it references and alters various fields of the ECA. To gain a better understanding of the interactions between the IMDC and the various ECA fields, the ECA data can be separated into four general categories.

- 1. Command, command status, and execution parameters

- 2. Programmable record processing fields

- 3. Disk Format Fields

- 4. Drive Control Parameters

These categories differentiate the ECA fields not only in content but in terms of the access and alterability.

2-466

## Command, Command Status and Execution Parameters

These parameters consist of the ECA data fields required by the IMDC to execute a command. The fields can be further separated into static fields and dynamic fields. The static fields are valid for the duration of a command; the IMDC does not alter any information in these fields as long as the command is being processed. The dynamic fields provide the 'local storage' needed to execute multiple sector commands. The IMDC uses the dynamic fields of the ECA to maintain the current execution status of the on-line disk drives.

## Table 5. ECA BLOCK FORMAT

| VORD NO. | 15 8                       | 7                     | 0   |

|----------|----------------------------|-----------------------|-----|

| 00       | Command code               | Main status           |     |

| 01       | Extende                    | d status              |     |

| 02       | Max # of retries           | Actual # of retries   |     |

| 03       | DMA count                  | Command options       |     |

| 04       | Buffer address mo          | st significant word   |     |

| 05       | Buffer address lea         | st significant word   |     |

| 06       | Buffer leng                | th request            |     |

| 07       | # of bytes                 | transferred           |     |

| 08       | Cylinder                   | number                | *   |

| 09       | Head number                | Sector number         | •   |

| 10       | Current cylin              | nder position         |     |

| 11       | PRP command                | d control word        | **  |

| 12       | Location of SCWT, r        | nost significant word | **  |

| 13       | Location of SCWT, I        | east significant word | **  |

| 14       | Scan terminator            | Reserved              | **  |

| 15       | Maximum rec                | ord length – 1        | **  |

| 16       | N0 – Pre index gap         | N1 - Post index gap   | *** |

| 17       | N2 - Sync byte count       | N3 – Post ID gap      | *** |

| 18       | N4 – Post data gap         | N5 - Address mark cnt | *** |

| 19       | Rese                       | erved                 | *** |

| 20 – 22  | ECC mask                   | (3 words)             |     |

| 23       | Motor on delay             | # of heads            |     |

| 24       | Ending sector #            | Stepping rate         |     |

| 25       | Head setting time          | Head load time        |     |

| 26       | Seek type                  | Phase count           |     |

| 27       | Low write Curren           | nt boundary track     |     |

| 28       | Precompensation            | boundary track        |     |

| 29 - 31  | ECC remaine                | ter (3 words)         | *** |

| 32       | Maximum number of          | cylinders per surface |     |

| 33       | First sector/sector length | Flag byte             |     |

| 34 – 35  | B-tree point               | ter (2 words)         | **  |

| 36 - 45  | IMDC wor<br>t0 w           | rking area<br>vords   |     |

\* Physical starting sector number.

\*\* Programmable record processing parameters.

\*\*\* Track format fields.

\*\*\*\* ECC remainder will be aligned to the MSB byte of this field.

#### Command Code (1 Byte)

The command code indicates the command to be executed. Table 6 lists the valid IMDC commands and their associated codes. For a complete description of each command refer to the command description in the Command section.

#### Main Status (1 Byte)

This field contains the general oriented status information about the command execution. This encoded byte is updated at the completion of the current command and before the interrupt is asserted. Table 7 shows the possible values which may be returned by the IMDC.

#### **Extended Status (2 Bytes)**

This field contains specific bit oriented status information about the command execution. If errors result during the execution, the corresponding bit will be ORed into extended status and kept there. This OR function can be used by the host system for error logging. The extended status will be reset to zero by

2-467

2

## Table 6. COMMAND CODES

|      | HEX<br>CODE | DESCRIPTION                    |

|------|-------------|--------------------------------|

| WRMS | 00          | Write multiple sector          |

| WRDD | 01          | Write with deleted data flag   |

| VER  | 10          | Verify                         |

| REMS | 11          | Read multiple sector           |

| PRP  | 12          | Programmable record processing |

| TSR  | 13          | Transparent sector read        |

| RETD | 20          | Read identifier                |

| FORM | 40          | Format                         |

| CALB | 41          | Recalibrate to track zero      |

| CORR | 81          | Correct data                   |

| DIAG | 80          | Diagnostic                     |

## Table 7. MAIN STATUS CODES

| DECIMAL  | DESCRIPTION                                                                                          |

|----------|------------------------------------------------------------------------------------------------------|

| 0        | Correct execution without error                                                                      |

| 1        | Irrecoverable error which cannot be completed (auto retries are at-<br>tempted, see extended status) |

| 2        | Drive not ready                                                                                      |

| з        | PRP operation unsuccessful                                                                           |

| 4 – 5    | Not used                                                                                             |

| 6        | Command rejected                                                                                     |

| 7 – 9    | Not used                                                                                             |

| 10       | Command abort (busy bit reset by host)                                                               |

| 11 – 255 | Not used                                                                                             |

#### Table 8. EXTENDED STATUS

| DATA BIT | DESCRIPTION                       |

|----------|-----------------------------------|

| 0        | Write fault                       |

| 1        | CRC/ECC error on data or ID       |

| 2        | FIFO overrun/underrun             |

| 3        | No identifier found               |

| 4        | Not used                          |

| 5        | Deleted data address mark         |

| 6        | Write on write protected diskette |

| 7        | Positioning error                 |

| 8        | Data part timeout                 |

| 9        | Not used                          |

| 10       | Uncorrectable data error (ECC)    |

| 11       | Not used                          |

| 12       | Not used                          |

| 13       | Positioning timeout               |

| 14       | Not used                          |

| 15       | Bus Error Fault (DMA operation)   |

This Material Copyrighted By Its Respective Manufacturer

#### the IMDC at the beginning of the command execution. The error definitions are shown in table 8.

#### Maximum Number of Retries (1 Byte)

This parameter specifies the maximum number of retries per command (not per sector) that the IMDC attempts, after a disk operation error. Loading a zero value indicates that no retries should be attempted. This byte will not be used if a bus error or FIFO under/overrun error occurs during the command execution. These two errors will cause an immediate command abort. If an identifier is not found, 16 revolutions of the disk will be tried before exit.

#### Actual Number of Retries (1 Byte)

This byte is set by the IMDC to the actual number of retries executed per command. All retries are accumulated by the IMDC on a sector by sector basis.

#### DMA Count (1 Byte)

This byte contains a DMA transfer count. If a zero value is specified, the IMDC transfers only one operand and surrenders the bus. A transfer amount of 1 to 16 can be specified.

#### Command Options (1 Byte)

This byte contains options that are to apply to the current command. Valid options for handling of deleted-data address marks are described in table 9. Sectors with the deleteddata address mark (bits 0, 1 of the option field) will be handled as shown for read operations, excluding those associated with the PRP command. Some retries may be necessary in these steps. They all start with a new identifier search.

#### Buffer Address

This is a 31-bit starting buffer address for the DMA transfers. The LSB of the address field defines the even or odd address of the 16 bit words when in 16-bit mode. For the 68000, only the first 23 bits are used for addressing. The additional bits can be used to implement the function codes. It should be noted that the IMDC does not protect the upper address lines, AD25 – AD31, from counter overflow. It is up to the operator to prevent transfers between the IMDC and memory greater than the 68000 addressing range. For PRP commands, this field contains the pointer to the content of the matched record data (see Programmable Record Processing section).

#### Buffer Length Requested (2 Bytes)

This field contains the requested number of bytes to be transferred. This field implicitly defines the number of multiple sector transfers to be performed. A seek only will occur when a zero length is specified. For the format track command, this value is used to terminate the operation.

#### Table 9. COMMAND OPTIONS

| BIT   | FORMAT | OPTION DESCRIPTION                                               |

|-------|--------|------------------------------------------------------------------|

| 1-0   | 00     | FM, IBM single density format                                    |

|       | 01     | MFM, IBM double density format                                   |

|       | 10     | Programmable disk format,                                        |

|       |        | 1 byte cylinder                                                  |

|       | 11     | Programmable disk format,                                        |

|       |        | 2 byte cylinder                                                  |

| 2     |        | Not used                                                         |

| 4 - 3 | 00     | Select CRC-CITT (CRC-16)                                         |

|       |        | polynomial                                                       |

|       | 01     | Select 32 bit ECC polynomial                                     |

|       | 10     | Select 40 bit ECC polynomial                                     |

|       | 11     | Not used                                                         |

| 5     | 0      | The sectors with deleted-data address mark will be skipped as    |

|       |        | if it did not exist. A successful CRC/ECC check is not required. |

| 1     | 1      | The data of the sector with deleted-data address mark will be    |

|       |        | transferred to the host system and the operation terminated      |

| 6     |        | Not used                                                         |

| 7     |        | Hard sectored disk                                               |

# Actual Number of Bytes Transferred (2 Bytes)

This field indicates how many bytes have been actually read or written during a command execution. The value can be used, for example, for a location of a problem sector with an irrecoverable error. The value of this field can be changed by the IMDC during the execution of a command and used as an intermediate field.

# Physical Starting Sector Number (4 Bytes)

Cylinder, head, sector – This field contains the physical disk sector location at which the command is to begin execution. The format of the field is shown below:

| Cylinder High | Cylinder Low  |  |

|---------------|---------------|--|

| Head Number   | Sector Number |  |

#### Current Cylinder (2 Bytes)

These two bytes will be updated by the IMDC after each positioning. At the beginning of the IMDC reset, they should be set by the host system to zero, because most of the hard disks have built-in automatic recalibration.

#### Programmable Record Processing Fields (10 Bytes)

The programmable record processing fields are described in the Programmable Record Processing section.

# Disk Track Format Fields (8 Bytes)

The disk track format fields are described in the Disk Track Format section.

#### ECC Mask (6 Bytes)

These six bytes define the error correction polynomial. The standard notation of a polynomial is:  $X^{40} + k_{39} X^{39} + \cdots + k_1 X' + k_0 X^0$

January 1986

The coefficients  $k_{39}$  through  $k_0$  may be any combination of 1s and 0s. For a given polynomial, an equal combination of bits in the mask register will initialize the IMDC logic to generate or check the same polynomial on the disk.

#### **Drive Control Parameters**

These fields contain information that define the disk interface to the IMDC. This information is provided by the host system and is not altered by the IMDC. The IMDC microprogram, that controls the disk drive I/O issued, continually references this information during the execution of a command. Because of the potentially large number of possible variations of interfaces, the IMDC cannot provide extensive verification of the parameters contained in these fields. Protection and verification of the a host operating system and not the IMDC.

#### Motor on Delay (1 Byte)

This field contains the motor on delay (period) in ten millisecond units. A value of zero represents a zero delay timeout.

Number of Heads (1 Byte) This value is the number of heads on the disk

unit. The maximum value is 128.

Ending Sector Number (1 Byte) This value is the last sector on the track (cylinder) for the disk unit.

#### Stepping Rate (1 Byte)

This field contains head stepping rate (period) in  $500\mu$ sec units if applicable.

#### Head Settling Time (1 Byte)

This field contains head settling time in 500µsec units. If a non-zero head settling time is specified, the IMDC assumes that a seek complete is not available from the drive.

2-469

#### Head Load Time (1 Byte)

This field contains head load time in 500µsec units. For all hard disks, this value must always be set to zero by the host system.

#### Seek Type (1 Byte)

This field defines what type of seek positioning is to be performed.

| VALUE | DESCRIPTION                 |

|-------|-----------------------------|

| 0     | Normal single step seek     |

| 1     | ST506 with accelerated seek |

| 2     | Disk with buffered seek     |

#### Phase Counter (1 Byte)

This field contains the phase counter which is a status of the command execution set by the IMDC.

# Low Write Current Active Track (2 Bytes)

This field defines, to the IMDC, the track at which low write current (LWC) output signal, on the output port (bit 8), is to be asserted.

#### Precompensation Active Track (2 Bytes)

This field defines to the IMDC the track at which precompensation signal (PRECOM) is to be asserted at the output port (bit 10).

#### ECC Remainder (6 Bytes)

This field contains the ECC remainder generated by the IMDC read operation. This returned value will be zero unless an error is detected.

#### Maximum Number of Cylinders (2 Bytes)

These bytes define, to the IMDC, the maximum cylinder count for the disk unit on line. If an operation is specified beyond this boundary, the IMDC will abort the command.

#### Sector Length (1 Byte)

This byte defines the sector length as a power of two multiple of 128 bytes, i.e., sector length =  $(2^{\pm})^*$  (128 bytes). The minimum sector length of 128 bytes is specified by a zero value while the maximum length of 4096 is specified by 5. The most significant bit of this byte is used for the IMDC's starting sector number, either 0 or 1. The three least significant bits are used for the sector length.

#### Flag Byte (1 Byte)

This byte is placed in the ECA by the IMDC during a transparent sector read (TSR) command operation. It is the flag byte for the data field part of the sector.

#### **B-Tree Pointer (4 Bytes)**

The IMDC loads the physical sector number of the last record match when in the PRP command mode and in the B-tree scan function (see the Programmable Record Processing section for further details).

## SCN68454

2

## SCN68454

#### IMDC Work Area (20 Bytes)

These ten words are reserved for the IMDC microprogram. The meaning of certain bytes of this area will be determined by the command being executed.

#### COMMANDS

The following is a generalized description of the sequence performed by the IMDC to execute a command:

- The IMDC checks if the drive is available. If it is not, the IMDC generates an error status and a completion interrupt.

- b. The IMDC executes a track seek if necessary. For drives which have a seek complete signal (as indicated by a zero value in the head settling time field of the ECA), a command termination can be caused by the timeout of the drive signal SEEK COMPLETE. Drives for which the head settling time is non-zero, the IMDC waits the specified time after issuing the stepping pulses (that is, there is no timeout on the seeks).

- The head will be selected, or for a floppy C. disk, loaded. The IMDC will wait four byte times to insure head switching has occurred.

- d. The IMDC reads the sector identifier to locate the requested sector. If the IMDC is unable to perform the sector identifier read, a retry is attempted for as many times as specified in the ECA maximum number of retries parameter. If the retries are all unsuccessful or if no retries are specified, the command is terminated (step q) and the status 'no identifier' is returned. If the matched sector identifier indicates a bad sector (see Track Format description), the IMDC uses the replacement information to perform steps b and c for the new sector. This bad sector replacement is not counted as a retry.

- After the requested sector has been located, the IMDC performs the sector disk I/O (read or write) and DMA operations. If the operation cannot be completed, the retry processing described in step d is attempted. A failure in this portion of the command is indicated by the return status 'data part time out', which distinguishes it from the read identifier failure of step d.

- f. If multiple sectors have been specified in the command, the IMDC assumes contiguous physical sectors: steps b, c, d and e are repeated for each sector. The IMDC automatically performs any track seek required if the next physical sector is located on the next cylinder. When the sectors are interleaved, the IMDC repeats step d until the correct sector is located.

In the case of a bad sector replacement,

January 1986

the IMDC continues the multiple sector operation, after the replacement sector, at the sector physically located after the bad sector. It performs all the necessary track repositioning required to return the drive head to the next physical sector.

Upon command completion, all relevant α. ECA fields are updated and the appropriate bits of the 'interrupt state status' and 'drive status and configuration' registers are set and an interrupt signal is generated by the IMDC. Upon interrupt acknowledge, the IMDC presents the interrupt vector from the interrupt vector register on the data bus.

#### **Command Description**

In the command descriptions, the term FIFO is used to refer to the internal memory of the IMDC when it is used as a FIFO buffer.

#### Write Multiple Sector with Implied Seek (WRMS)

After the desired sector is located, the IMDC will write the complete data part; preamble, address mark, flag, data, CRC or ECC and postamble. The precise format is given by the drive type. The FIFO will be continuously filled with the new data from the buffer. The number of data bytes written in one sector is determined by the IMDC using information from the ECA fields. This operation is repeated until the number of sectors, implied by the buffer length field of the ECA, have been written.

#### Write with Deleted Word (WRDD)

This command differs from the normal write only in that the flag or address mark written is the deleted data address mark or flag.

#### Verify (VER)

Verify with implied seek is the same functionally as the read command, except the IMDC compares the ECC or the CRC for accuracy. No data is transferred to the system.

#### **Read Multiple Sector with Implied Seek** (REMS)

After a successful seek to the desired sector. the IMDC will start to read the data of the sector, fill the FIFO buffer and check the CRC or ECC code. This sector data is transferred through the DMA interface to the host system memory. This procedure is repeated until the number of sectors, implied by the buffer length field of the ECA, have been read. For sectors with the deleted data address mark. the IMDC will process them according to the options selected in the command option field of the ECA.

#### Programmable Record Processing (PRP) Refer to the Programmable Record Processing section.

#### Transparent Sector Read (TSR)

This command will read a single error sector and transfer the data to the FIFO buffer 2-470

regardless of a CRC or ECC check. Only the extended status will be correspondingly filled with all errors encountered. The transparent sector read can be used for diagnostic purposes and, with some manual help, for recovery of damaged data. In case of an incorrect CRC/ECC remainder, the IMDC discards the remainder into four bytes reserved in the ECA for this value.

#### Read Identifier (RETD)

This command will read identifiers as they come from the disk and fill the whole buffer with records consisting of:

- flag byte

- ID data

- CRC

- remainder generated by IMDC

A CRC error will not terminate the execution of the command. For soft sectored formats, the command execution will begin and end with the detection of an index pulse. For the hard sectored formats, the IMDC will detect and count sector pulses to determine the command termination.

#### Format a Track with Implied Seek (FORM)

The IMDC supports four different media formats (see Disk Track Format section). This command allows the user to write the format information, as specified by the ECA track format fields, to the recording media.

#### **Recalibrate to Track Zero (CALB)**

The function of this command is to retract the heads to track 0. The IMDC issues one step 'IN' and then steps 'OUT' until the signal track 0 becomes active or the maximum number of steps equal the number of cylinders from the ECA. The check on seek completed timeout will be made for the hard disk. The function recalibrate can be initiated automatically by two conditions:

- Encountered error in cylinder number by reading or writing.

- Writing zero into the current cylinder in ECA.

#### Correct (CORR)

This command provides an error mask which is used to correct the data in the memory. It uses the ECC remainder field of the ECA. The IMDC will put the error correction vector and its relative position from the end of the data buffer into the ECA.

The 24-bit ECC correction mask will be placed in the flag byte and first half of the Btree pointer of the ECA block. This is the least significant byte of the 33rd word and the 34th word of the ECA block in memory as shown in table 5. The offset count will be placed in the second half of the B-tree pointer or the 35th word of the ECA block. This is the relative offset from the last byte transferred to memo-

SCN68454

# Intelligent Multiple Disk Controller (IMDC)

ry, plus four for a 32-bit ECC or five for a 40bit ECC.

#### Chip Diagnostic (DIAG)

The IMDC will exercise the 16-bit counters; the record counter, the record length counter, the buffer length counter, and the time out counter. If everything is functioning properly, the IMDC places a zero byte into the main status. Otherwise, an irrecoverable error bit value is set in the main status.

#### DISK TRACK FORMAT

The IMDC supports four different track formats:

- IBM 3740 single density

- IBM System 34 double density

- Programmable soft sectored

- Programmable hard sectored

In each of the formats, data on the physical media is separated into blocks of information or sectors. The format serves several purposes in this arrangement; it defines the structure of the sector, the location of the actual data, and provides gaps and sync bytes that allow an interval for any switching required by the drive hardware. These intervals, in turn, allow the IMDC to compensate for any variations in either the recording media and/or the drive hardware. Although each of these formats is well defined, variations of parameter values within a given format require that the IMDC provide the user with the capability to program them.

Because there is no one standard which defines track format parameters, a description of them and other pertinent definitions are included in this section. See table 10 for track format definitions. Tables 11 and 12 provide a summary of the formats and the

programmable values. The following definitions apply:

The format command operation is performed by the IMDC as integral operations on a per track basis, as opposed to normal disk I/O which is on a sector basis. This technique was selected as a compromise to satisfy two conflicting - requirements command efficiencv versus equal access of on-line drives to the IMDC resources. Obviously, these commands would be most efficient if allowed to monopolize the IMDC resources. However, this situation would prevent any other drive from being serviced until the command had been completed. Normally these commands are background tasks with the other disk operations having a higher priority. For this reason, allowing the IMDC to concentrate completely on either command is not a good system practice.

The IMDC becomes available for other processing after a full track has been processed. In the worst case situation for the format command, the time the IMDC will not be able to process the other drives will not exceed two disk revolutions. This would occur for disks in which the index pulse was just missed and a complete revolution is required to find the pulse.

The programmable soft sectored disk format, which is used mainly for hard disk drives, is a MFM format which is nearly identical to the IBM double density format. The hard sectored disk format is used for rigid disks with an internal sector clock and is similar to the soft sectored format, except that each sector starts with the sector pulse rather than a related byte count from the index pulse. The format track command allows the user to write formatting information to the recording media. Specification of format parameters is accomplished by changing appropriate ECA fields. This structure gives the user a tremendous flexibility to accommodate, through changes in the ECA, variations that occur within a given format.

For non-hard sectored disk formats, the IMDC writes the sector identifier and fills the data part with the fill byte starting with the leading edge of the first index pulse and ending with the leading edge of the next index pulse. For hard sectored disk formats, the format information is written between sector pulses.

Tables 11 and 12 show the possible layout of the track information in table format. Table 11 is for the floppy parameters and table 12 is for the rigid disk format parameters. In table 11 each of the different fields on each track is described. Associated with each field is where the IMDC gets the data, either from the ECA register locations or through the DMA process from the system memory.

#### **ECA Track Format Fields**

For the four formats supported by the IMDC, eight parameters are required to specify the format of the recording media to the IMDC. The format parameters are programmed by changing the values of the appropriate ECA fields. The layout of the track format portion of the ECA is given in table 13.

N0 and N1 are ignored by the hard sectored format and only N1 is applicable to the programmable soft sectored format. N5 contains the number of address marks contained in the address mark subfields for the active

| NAME | SUBFIELD | FORMATS                 | DESCRIPTION                                                                                                                                                                                   |

|------|----------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO   | Index    | IBM only                | Pre-index Gap. This gap represents the number of bytes that appear prior to the index pulse.                                                                                                  |

| N1   | Index    | All except<br>hard sect | Index Gap. This gap represents the number of bytes that appear after the index pulse and prior to the ID subfield.                                                                            |

| N2   | ID, data | All                     | Preamble count or sync. This is the number of index sync bytes that precede the address mark.                                                                                                 |

| N3   | ID       | All                     | Post ID gap. This count is the number of bytes that separate the ID subfield from the data subfield.                                                                                          |

| N4   | Data     | All                     | Post data gap. This count is the number of bytes that separate<br>the data subfield to the beginning of the ID subfield of the next<br>sector.                                                |

| N5   | ID, data | iBM                     | Address Mark Count. This contains the number of index address<br>marks contained by the subfields. For single density formats, the<br>count is one and for double density the count is three. |

|      | ID, data | Prog                    | The number of data part address marks is a 1, 2 or 3. The num-<br>ber of ID address marks is always 1.                                                                                        |

Table 10. TRACK FORMAT DEFINITIONS

## SCN68454

## Table 11. SUMMARY OF FLOPPY FORMAT PARAMETERS

| DESCRIPTION                                                                                                                 | IMDC<br>USES                         | HEX DATA<br>VALUE                                      | FM CNT                                | HEX DATA<br>VALUE                                    | MFM CNT                                |                       |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------|---------------------------------------|------------------------------------------------------|----------------------------------------|-----------------------|

| Pre-index gap<br>Sync field<br>Index mark<br>Index flag<br>Index gap                                                        | N0<br>N2<br>N5<br>N1                 | FF<br>00<br>FC/D7 <sup>1</sup><br>-<br>FF              | 40<br>6<br>1<br>-<br>26               | 4E<br>00<br>C2 <sup>2</sup><br>FC<br>4E              | 80<br>12<br>3<br>1<br>50               |                       |

| Sync field<br>ID address mark<br>ID address flag<br>Cylinder<br>Side<br>Sector<br>Record length<br>CRC-CCITT<br>Post ID gap | N2<br>DMA<br>DMA<br>DMA<br>DMA<br>N3 | 00<br>FE/C7 <sup>1</sup><br>-<br>01 <sup>4</sup><br>FF | 6<br>1<br>1<br>1<br>1<br>1<br>2<br>11 | 00<br>A1 <sup>3</sup><br>FE<br>01 <sup>4</sup><br>4E | 12<br>3<br>1<br>1<br>1<br>1<br>2<br>22 | Repeat as<br>required |

| Sync field<br>Data address mark<br>Data address flag<br>DATA (see note 4)<br>CRC-CCITT<br>Post data gap                     | N2<br>N5<br>N4                       | 00<br>FB/C7 <sup>1</sup><br>Fill byte<br>FF            | 6<br>1<br>-<br>256<br>2<br>27         | 00<br>A1 <sup>3</sup><br>FB<br>Fill byte<br>4E       | 12<br>3<br>1<br>256<br>2<br>54         | <b>•</b>              |

| Inter-record gap5                                                                                                           |                                      | FF                                                     | 170                                   | 4E                                                   | 598                                    |                       |

#### NOTES:

1. Shows data pattern and clock pattern (clock pattern normally FF).

2. Shows data pattern; clock pattern should suppress clock bit between data bit

3 and 4.

Shows data pattern; clock pattern should suppress clock bit between data bit 4 and 5.

4. This example is for a 256 byte sector, others will have different values.

5. This is an approximate count.

## Table 12. SUMMARY OF RIGID FORMAT PARAMETERS

|                                                                                                                        |                                     | HARD SECTOR                                                    |                                     | SOFT SECTOR                                                    |                                     |                       |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------|-------------------------------------|-----------------------|

| DESCRIPTION                                                                                                            | USES                                |                                                                | Pgm Cnt                             | Hex Data<br>Value                                              | Pgm Cnt                             |                       |